以下是文章内容:

【基本信息】

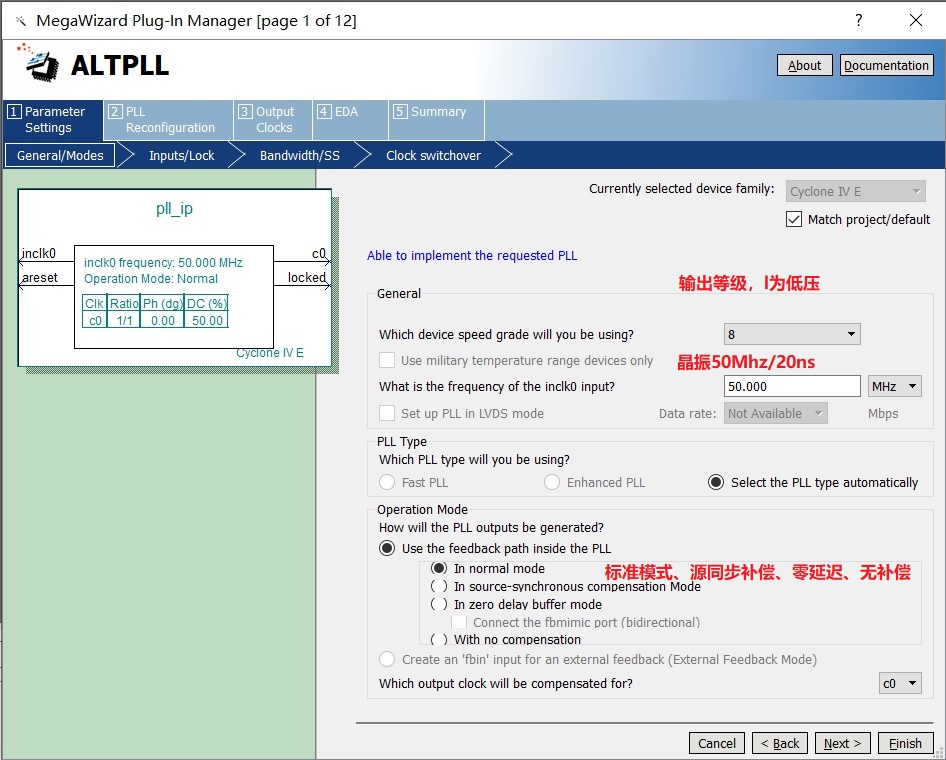

要求:使用PLL—IP核,输入50Mhz晶振,输出四路不同信号:100Mhz,25Mhz,50Mhz(90°相位),50Mhz(20%占空比)。

芯片型号:cyclone Ⅳ EP4CE10F17C8

平台工具:Quartus II 15.0 (64-bit)、Modelsim SE-64 10.4

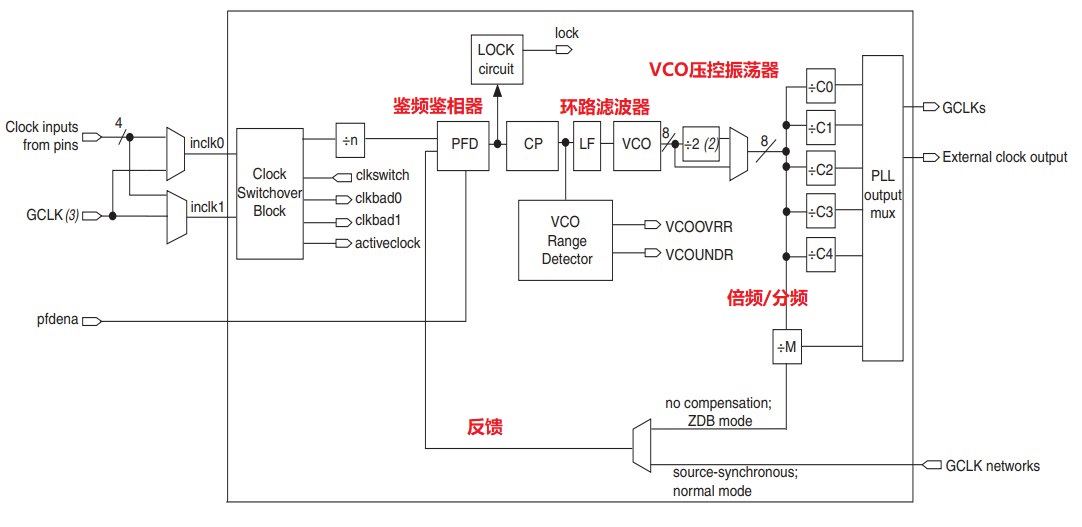

【PLL_IP核简介】

IP核是ASIC或FPGA中预先设计好具有某种功能的电路模块,参数可修改,目的在于提高开发效率。QuartusII软件下IP核调用方式:Mega Wizard插件管理器(常用)、SOPC构造器、DSP构造器、Qsys设计系统例化。PLL(Phase Lockded Loop,锁相环)是常用的IP核之一,可对输入时钟信号进行任意分频、倍频、相位、占空比调整。

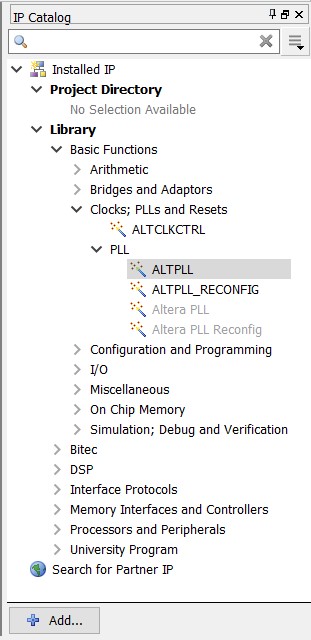

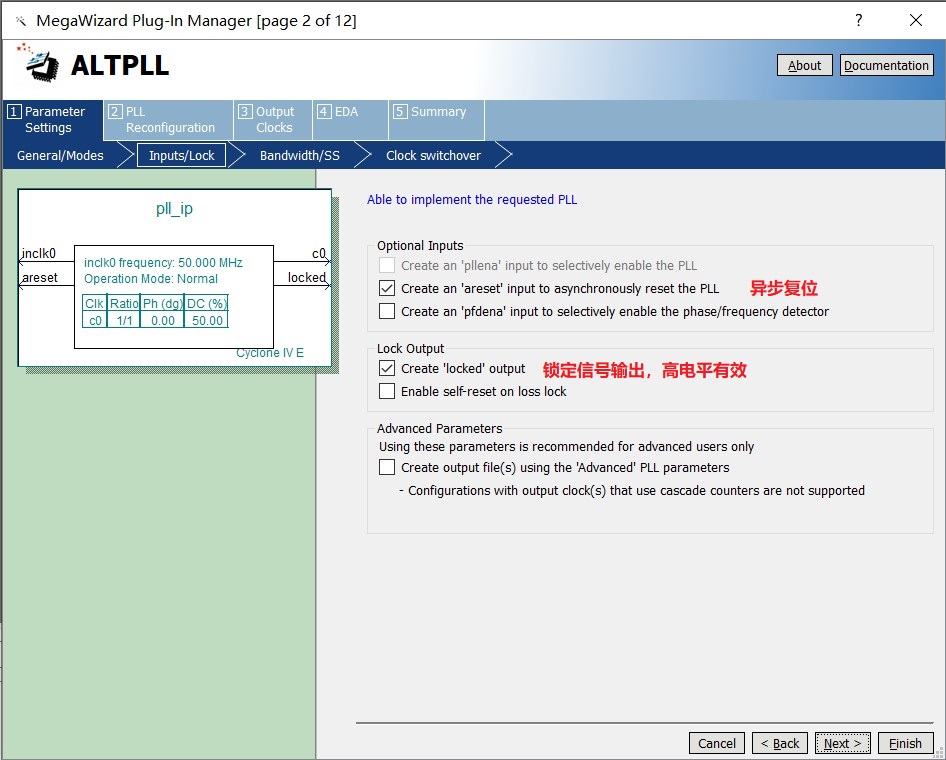

【PLL_IP核配置】

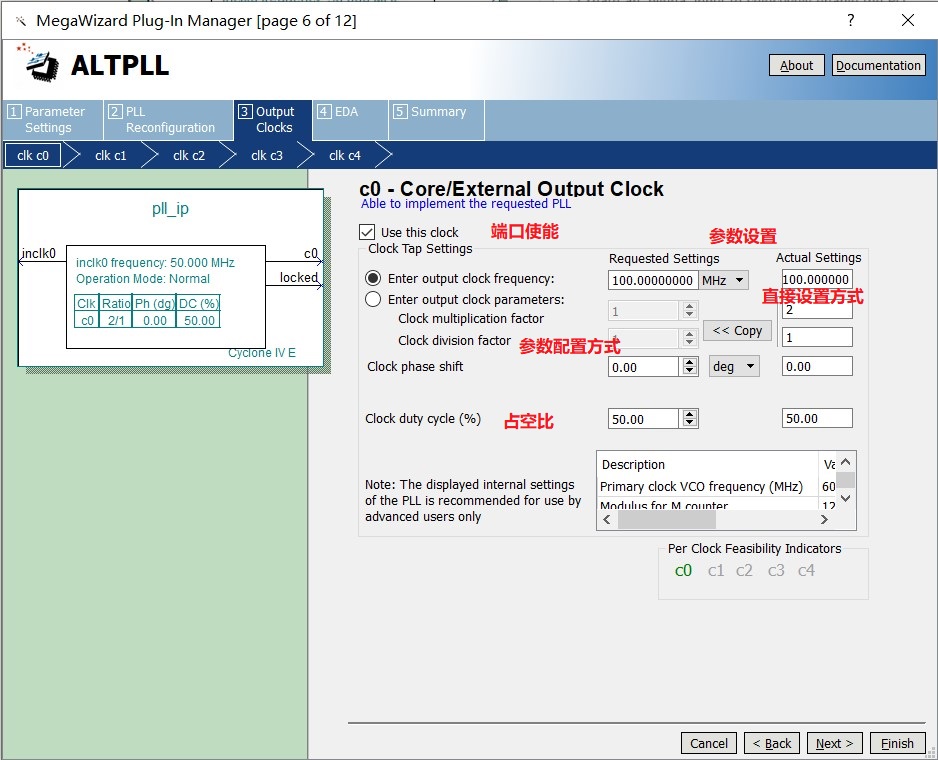

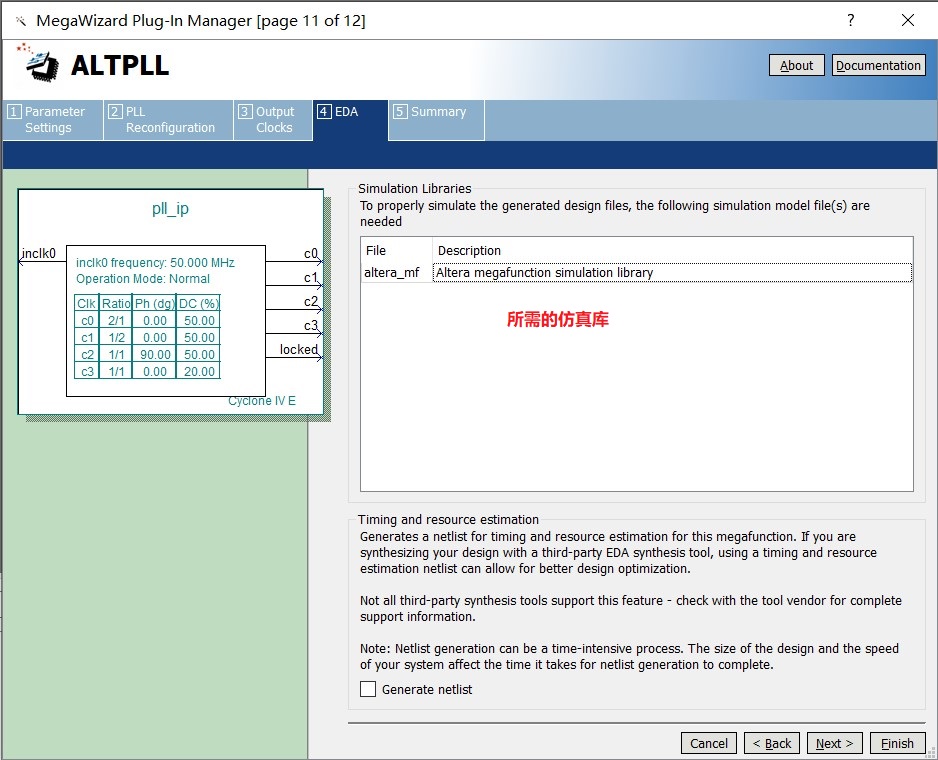

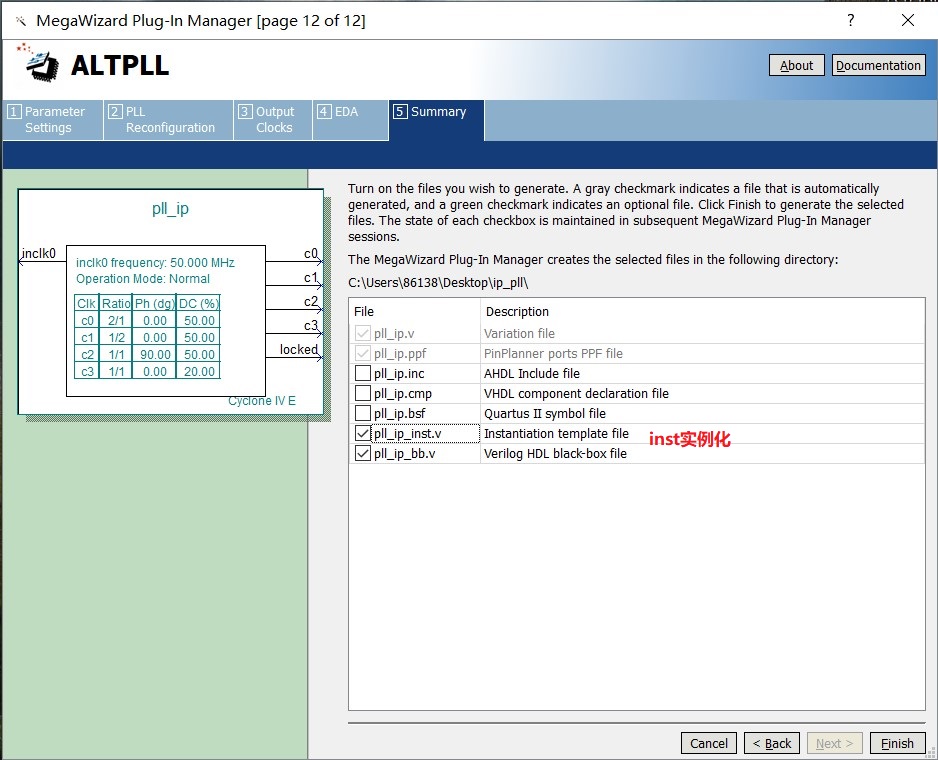

进入QuartusII,直接打开Mega Wizard插件管理器或者打开工具菜单栏下IP—catalog,选择PLL-ALTPLL。配置包括参数/模式设置、信号输入和锁定输出设置、Bandwidth/CSS和时钟切换设置、PLL Reconfiguration动态/动态相位重配置设置、输出时钟信号配置。配置完成后,可以看到PLL_IP产生了四路时钟信号和一路锁定信号。

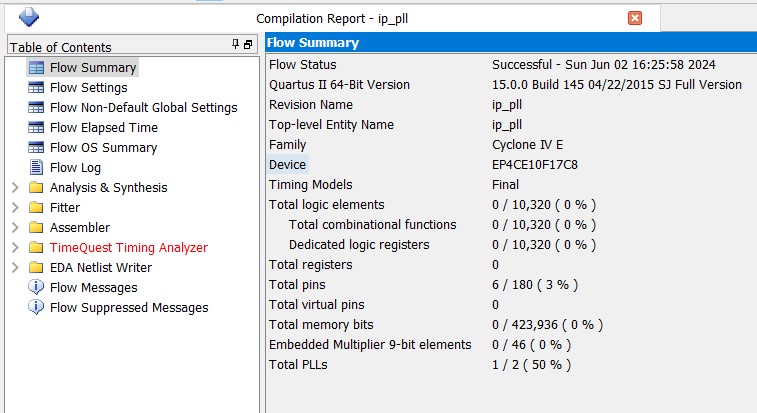

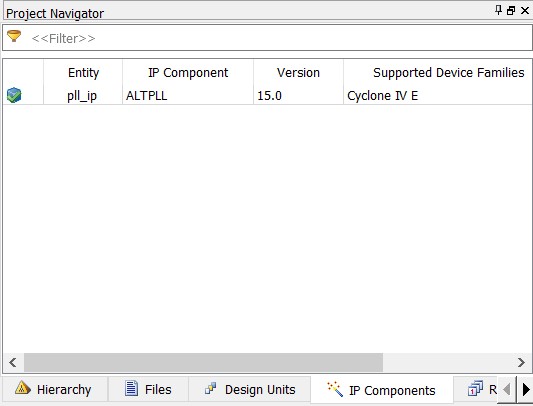

【PLL_IP核调用】

PLL_IP核编辑好后,可以通过引脚配置进行上机测试输出。对工程文件全编译,可以查看芯片资源的使用情况。PLL_IP核调用后,可以使用两种方式进行后期修改:在Quartus主页左上方Project Navigator-IP ComPONEnts双击打开目标IP核,或者在Mega Wizard插件管理器选择编辑现有IP核。如果不小心把IP核删除了,只需重新添加目标IP核文件,后缀.qip(主文件)添加应用。需要复制现有IP核,只需打包IP核文件,后缀包括.v;inst.v;.qip;.ppf;greybox_tmp五个文件,然后添加应用到工程文件。

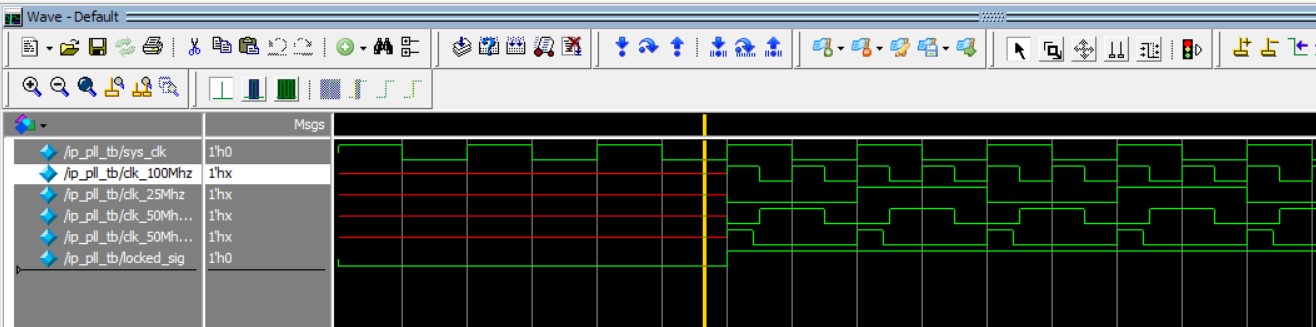

【PLL_IP核仿真】

在仿真结果中,可以观察到锁相环的锁定过程。在这个过程中,锁相环的输出信号(locked信号)会保持低电平状态,表示锁相环尚未锁定,各时钟信号输出会处于不定态,它们的值会随机变化或保持不变。稳定后,可以明显看到频率、相位、占空比的调整情况。

Ps:如需要工程重要的文件,在个人博客首页Gitee仓库内可以得到。